## Silicon Quantum Dot Superlattices for High Efficiency Thermoelectrics

#### Bingyuan Huang, Xiao Guo, Duck Hyun Lee, Peter F. Green and Akram I. Boukai

Department of Materials Science and Engineering, University of Michigan, Ann Arbor, MI

#### Project Overview

- Advantages of silicon as a thermoelectric material.

- High abundance on the Earth.

- Less toxic than other thermoelectric materials, e.g., Pb, Bi, Te.

- Better integration with electric devices.

- > Thermoelectric figure of merit

$$ZT = \frac{S^2 \sigma}{\kappa} T$$

, Power Factor =  $S^2 \sigma$

- S thermopower,  $\sigma$  electrical conductivity,  $\kappa$  thermal conductivity, T temperature

- At room temperature, ZT of bulk silicon is only ~0.01.

- Control S,  $\sigma$  and  $\kappa$  independently.

- > Decrease the thermal conductivity using nanostructures.

- As feature dimensions shrink to the phonon mean free path (~300nm), strong scattering of phonons should occur and  $\kappa$  decreases. In the meantime, the electrical conductivity is not heavily affected.

- > Increase the electrical conductivity using crystal lattice strain.

- Lattice strain affect the curvature of the energy band, resulting in lower effective mass of charge carriers and consequently higher mobility and conductivity.

- In this work, nanomesh structure was made on strained silicon thin films.

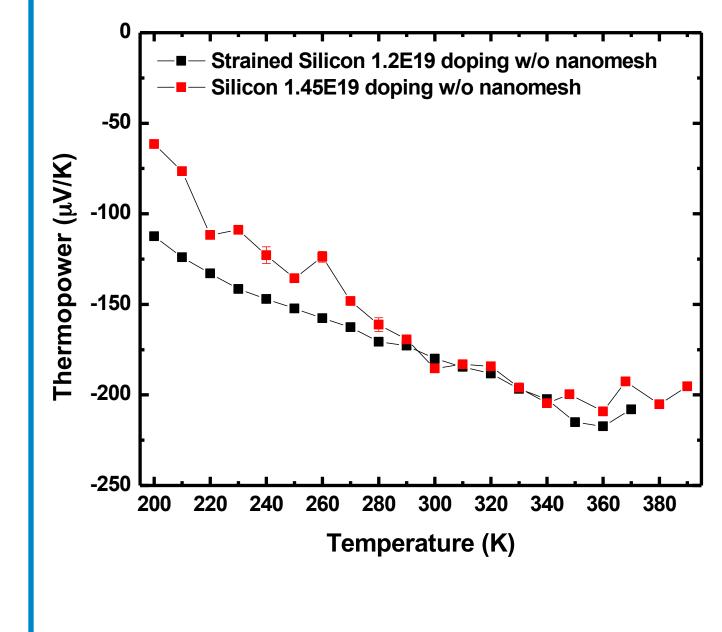

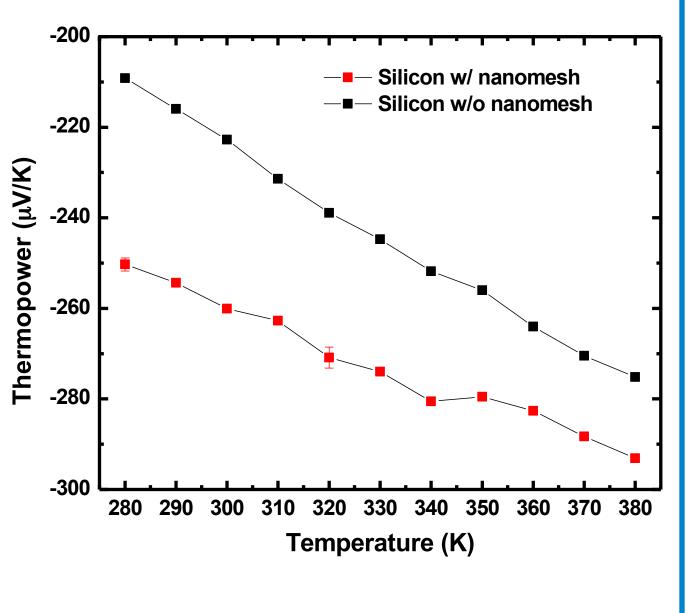

- Thermopower values were enhanced for both strained silicon and normal silicon by adding nanomesh.

- Strained silicon showed higher electrical conductivity than hofrata 39966n.

#### Device Fabrication

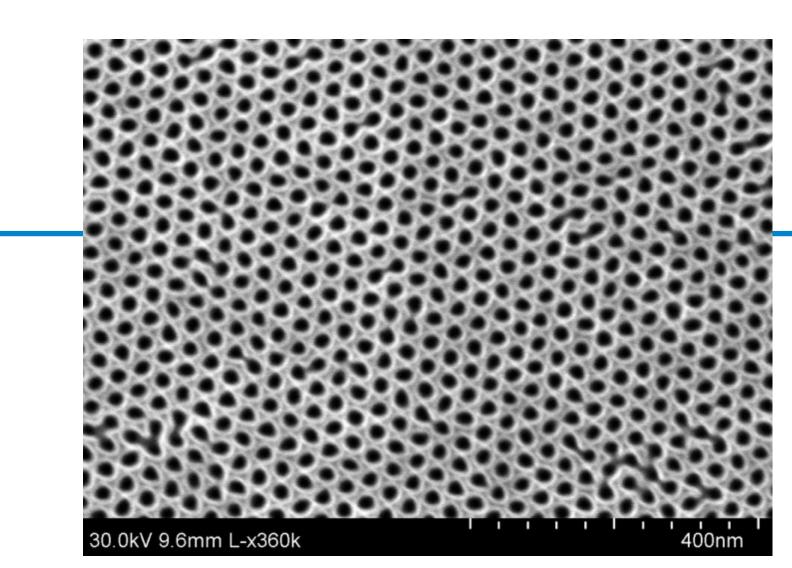

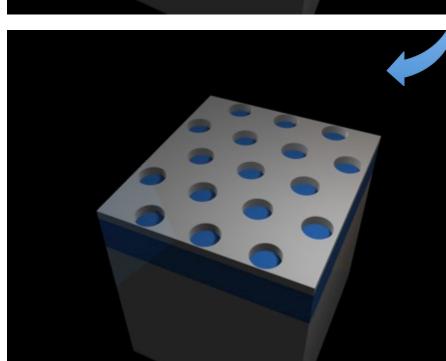

- Nanomesh is made on the strained silicon thin film on SiO<sub>2</sub> through steps as shown in the right schematics.

- PS-PMMA block copolymer layer is first spincoated on top of the strained silicon.

- After annealing and UV treatment, PMMA is removed by acetic acid.

- Nanomesh is imprinted into strained silicon thin film by DRIE through the PS mask.

- PS is finally removed by Piranha cleaning.

- SEM images show almost perfect hexagonal nanomesh on the strained silicon.

Top view. nearly 20nm with pitches about 40 nm.

### Thermopower Characterization

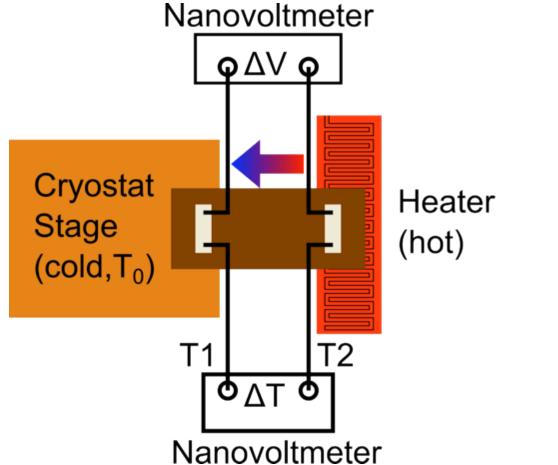

> All thermopower measurements were conducted in a cryostat using a LabVIEW interface.

> A schematic of the experimental setup.

A screenshot of the LabVIEW program

> Thermopower is improved by adding nanomesh for both strained silicon and normal silicon. *Raw data* Linear fitting

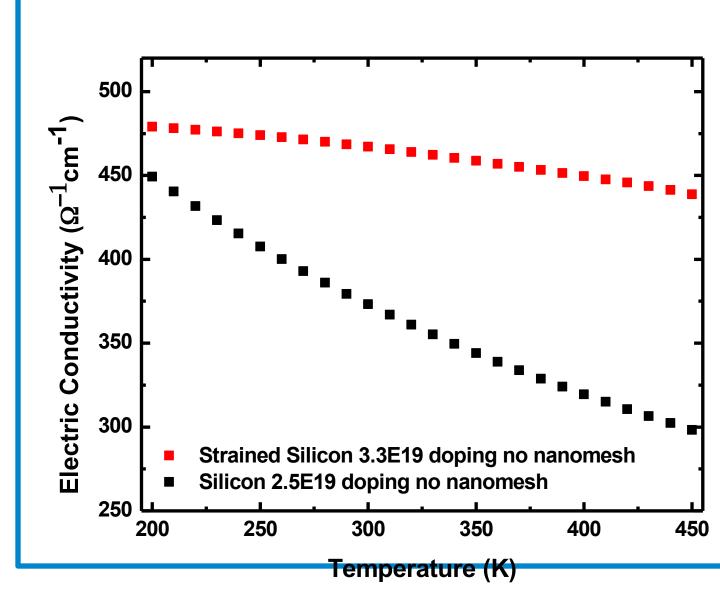

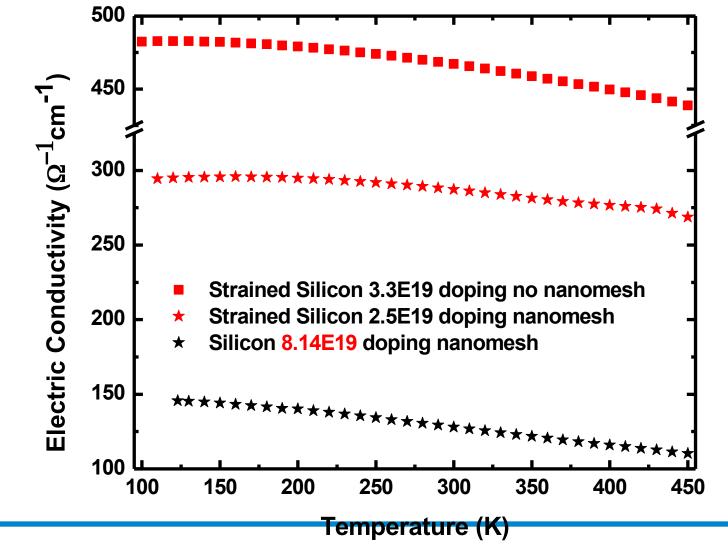

### Electrical Conductivity Characterization

- Electrical conductivity were measured in a cryostat using a four-point setup.

- Strained silicon shows much higher electrical conductivity than normal silicon, both with and without nanomesh.

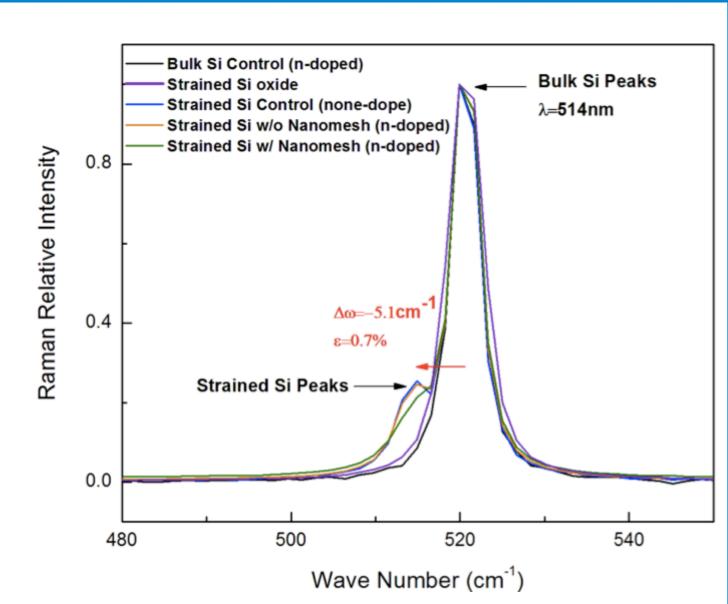

# Raman Spectroscopy

Raman spectroscopy was conducted to verify that nanomesh didn't release all lattice strain in the strained silicon.

> The green curve indicates that the nanomesh did release some lattice strain. However, most strain is still retained.